## Atmel AT42QT2160

## 16-key QMatrix Touch Sensor IC

## DATASHEET

### **Features**

- Number of keys:

- up to 16 keys, and one slider (constructed from 2 to 8 keys)

- Technology:

- patented spread-spectrum charge-transfer (transverse mode)

- Number of I/O lines:

- 11 (3 dedicated configurable for input or output, 8 shared output only)

- PWM control for LED driving

- Key outline sizes:

- 6 mm × 6 mm or larger (panel thickness dependent); widely different sizes and shapes possible

- Key spacings:

- 8 mm or wider, center to center (panel thickness dependent)

- Slider design:

- 2 to 8 keys placed in sequence, same design as keys

- Electrode design:

- two-part electrode shapes (drive-receive); wide variety of possible layouts

- PCB layers required:

- one layer (with jumpers), two layers (no jumpers)

- Electrode materials:

- PCB, FPCB, silver or carbon on film, ITO on film

- Panel materials:

- plastic, glass, composites, painted surfaces (low particle density metallic paints possible)

- Adjacent metal:

- compatible with grounded metal immediately next to keys

- Panel thickness:

- up to 3 mm glass, 2.5 mm plastic (key size dependent)

- Key sensitivity:

- individually settable via simple commands over I<sup>2</sup>C-compatible interface

- Interface:

- I<sup>2</sup>C-compatible slave mode (100 kHz)

- Moisture tolerance:

- Increased moisture tolerance based on hardware design and firmware tuning

- Signal processing:

- self-calibration, auto drift compensation, noise filtering

- Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology

- Applications:

- Laptop, mobile, consumer appliances, PC peripheral

- This datasheet is applicable to revision 4R0 chips only

- Operating Voltage:

- 1.8 V 5.5 V

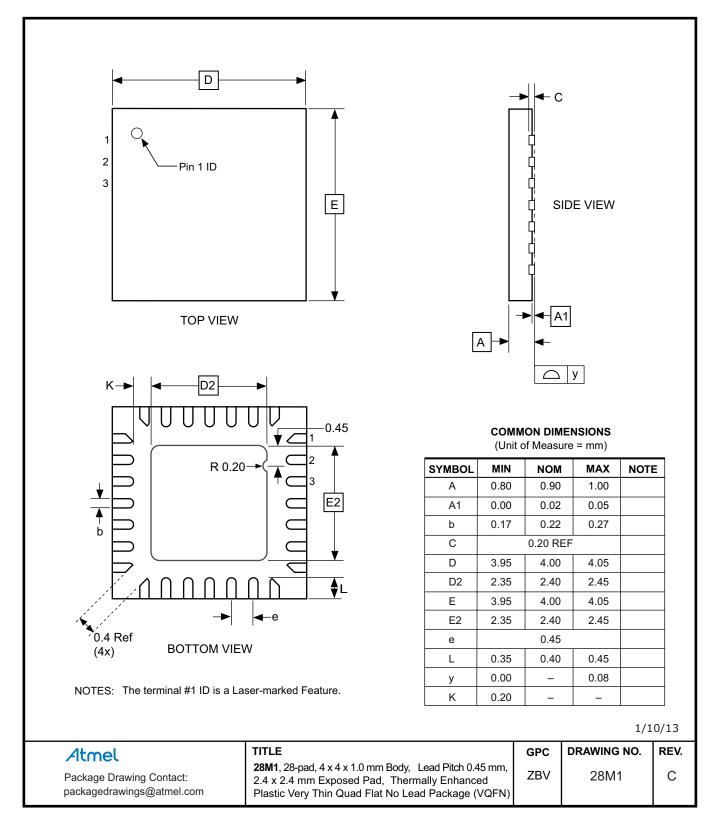

- Package:

- 28-pin 4 × 4 mm QFN RoHS compliant

## 1. Pinout and Schematic

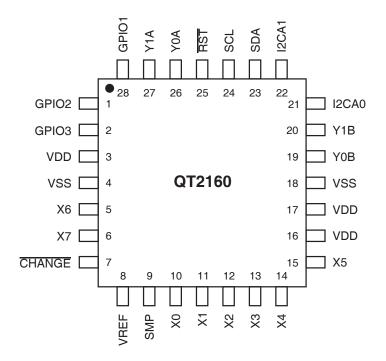

## 1.1 Pinout Configuration

## 1.2 Pinout Descriptions

#### Table 1-1. Pin Listing

| Pin | Name   | Туре | Comments                            | If Unused, Connect<br>To… |

|-----|--------|------|-------------------------------------|---------------------------|

| 1   | GPIO2  | I/O  | General purpose input/output 2      | -                         |

| 2   | GPIO3  | I/O  | General purpose input/output 3      | -                         |

| 3   | Vdd    | Р    | Power                               | -                         |

| 4   | Vss    | Р    | Supply ground                       | -                         |

| 5   | X6     | 0    | X matrix drive line / shared GPO X6 | Leave open                |

| 6   | X7     | 0    | X matrix drive line / shared GPO X7 | Leave open                |

| 7   | CHANGE | OD   | State change notification           | Leave open                |

| 8   | Vref   | Р    | Supply ground                       | -                         |

| 9   | SMP    | 0    | Sample output.                      | -                         |

| 10  | X0     | 0    | X matrix drive line / shared GPO X0 | Leave open                |

| 11  | X1     | 0    | X matrix drive line / shared GPO X1 | Leave open                |

## Table 1-1. Pin Listing (Continued)

| Pin | Name  | Туре | Comments                                  | If Unused, Connect<br>To… |

|-----|-------|------|-------------------------------------------|---------------------------|

| 12  | X2    | 0    | X matrix drive line / shared GPO X2       | Leave open                |

| 13  | Х3    | 0    | X matrix drive line / shared GPO X3       | Leave open                |

| 14  | X4    | 0    | X matrix drive line / shared GPO X4       | Leave open                |

| 15  | X5    | 0    | X matrix drive line / shared GPO X5       | Leave open                |

| 16  | Vdd   | Р    | Power                                     | -                         |

| 17  | Vdd   | Р    | Power                                     | -                         |

| 18  | Vss   | Р    | Supply ground                             | -                         |

| 19  | Y0B   | I/O  | Y line connection                         | Leave open                |

| 20  | Y1B   | I/O  | Y line connection                         | Leave open                |

| 21  | I2CA0 | I    | I <sup>2</sup> C address select           | -                         |

| 22  | I2CA1 | I    | I <sup>2</sup> C address select           | -                         |

| 23  | SDA   | OD   | Serial Interface Data                     | -                         |

| 24  | SCL   | OD   | Serial Interface Clock                    | -                         |

| 25  | RST   | I    | Reset low; has internal 30k - 60k pull-up | Leave open or Vdd         |

| 26  | Y0A   | I/O  | Y line connection                         | Leave open                |

| 27  | Y1A   | I/O  | Y line connection                         | Leave open                |

| 28  | GPIO1 | I/O  | General purpose input/output 1            | -                         |

I Input only OD Open drain ou 0

Open drain output P

Output only, push-pull Ground or power

I/O I

Input/output

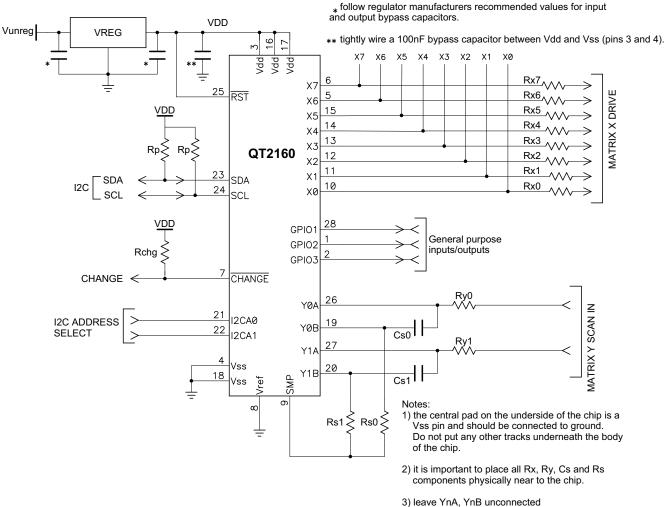

## 1.3 Schematic

#### Figure 1-1. Typical Circuit

if not used.

Check the following sections for component values:

- Section 3.3 on page 8: Cs capacitors (Cs0 Cs1)

- Section 3.5 on page 10: Sample resistors (Rs0 Rs1)

- Section 3.7 on page 10: Matrix resistors (Rx0 Rx7, Ry0 Ry1)

- Section 3.11 on page 15: Voltage levels

- Section 5.4 on page 22: SDA, SCL pull-up resistors (Rp)

- Section 5.5 on page 22: CHANGE resistor (Rchg)

- Section 5.2 on page 21: I<sup>2</sup>C addresses

## 2. Overview

## 2.1 Introduction

The AT42QT2160-MMU (QT2160) is designed for use with up to 16 keys and a slider (constructed from 2 keys up to 8 keys). There are three dedicated General Purpose Input/Outputs (GPIOs) which can be used as inputs for mechanical switches or as driven outputs. There are eight shared General Purpose Outputs (GPOs) (X0 - X7) which are driven outputs only. There is PWM control for each GPIO/GPOs.

The QT2160 device is a digital burst mode charge-transfer (QT<sup>™</sup>) sensor designed specifically for matrix layout touch controls; it includes all signal processing functions necessary to provide stable sensing under a wide variety of changing conditions. Only a few external parts are required for operation. The entire circuit can be built within a few square centimeters of single-sided PCB area. CEM-1 and FR1 punched, single-sided materials can be used for the lowest possible cost. The PCB rear can be mounted flush on the back of a glass or plastic panel using a conventional adhesive, such as 3M VHB two-sided adhesive acrylic film.

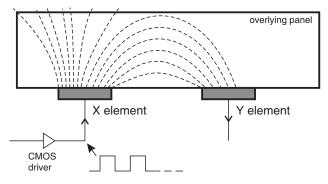

The QT2160 technology employs transverse charge-transfer sensing electrode designs which can be made very compact and are easily wired. Charge is forced from an emitting electrode into the overlying panel dielectric, and then collected on a receiver electrode (see Figure 2-1). This directs the charge into a sampling capacitor which is then converted directly to digital form, without the use of amplifiers.

The keys are configured in a matrix format that minimizes the number of required scan lines and device pins. The key electrodes can be designed into a conventional Printed Circuit Board (PCB) or Flexible Printed Circuit Board (FPCB) as a copper pattern, or as printed conductive ink on plastic film.

The device uses an I<sup>2</sup>C-compatible interface to allow key data to be extracted and to permit individual key parameter setup. The command structure is designed to minimize the amount of data traffic while maximizing the amount of information conveyed.

In addition to normal operating and setup functions the device can also report back actual signal strengths.

## Figure 2-1. Field Flow Between X and Y Elements

## 2.2 Keys and Slider

The QT2160 is capable of a maximum of 16 keys. These can be located anywhere within an electrical grid of eight X and two Y scan lines.

A lesser number of enabled keys will cause any unused acquisition burst time slots to be pared from the sampling sequence, to optimize acquire speed and lessen power consumption. Thus, if only eight keys are actually enabled, only eight timeslots are used for scanning.

Additional processing can be done on the keys to form a slider. The slider must start at X0 and use only Y0. The slider can consist of a minimum of two keys and a maximum of eight keys.

## 2.3 Enabling/Disabling Keys

Keys can be enabled by setting a non-zero burst length. A zero burst length disables the key.

## 2.4 Moisture Tolerance

The presence of water (condensation, sweat, spilt water, and so on) on a sensor can alter the signal values measured and thereby affect the performance of any capacitive device. The moisture tolerance of QTouch devices can be improved by designing the hardware and fine-tuning the firmware following the recommendations in the application note Atmel *AVR3002: Moisture Tolerant QTouch Design* (www.atmel.com/Images/doc42017.pdf).

## 3. Hardware and Functional

## 3.1 Matrix Scan Sequence

The circuit operates by scanning each key sequentially, key by key. Key scanning begins with location X = 0, Y = 0 (key 0). X axis keys are known as *rows* while Y axis keys are referred to as *columns* although this has no reflection on actual wiring. Keys are scanned sequentially by row, for example the sequence X0Y0 X1Y0 ... X7Y0, X0Y1, X1Y1... and so on. Keys are also numbered from 0 - 15. Key 0 is located at X0Y0. Table 3-1 shows the key numbering.

|    | X7 | X6 | X5 | X4 | Х3 | X2 | X1 | X0 |         |

|----|----|----|----|----|----|----|----|----|---------|

| Y0 | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  | Key     |

| Y1 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | numbers |

Table 3-1. Key Numbers

Each key is sampled in a burst of acquisition pulses whose length is determined by the Setups parameter BL (Table 7-1 on page 36); this can be set on a per-key basis. A burst is completed entirely before the next key is sampled; at the end of each burst the resulting signal is converted to digital form and processed. The burst length directly impacts key gain; each key can have a unique burst length in order to allow tailoring of key sensitivity on a key-by-key basis.

## 3.2 Burst Paring

Keys that are disabled by setting their burst length to zero have their bursts removed from the scan sequence to save scan time and thus power. The QT2160 operates on a fixed 16 ms cycle and will go to sleep after all acquisitions and processing is done till the next 16ms cycle starts. As a consequence, the fewer keys, the less power is consumed.

## 3.3 Cs Sample Capacitor Operation

Cs capacitors (Cs0 – Cs1) absorb charge from the key electrodes on the rising edge of each X pulse. On each falling edge of X, the Y matrix line is clamped to ground to allow the electrode and wiring charges to neutralize in preparation for the next pulse. With each X pulse charge accumulates on Cs causing a staircase increase in its differential voltage.

After the burst completes, the device clamps the Y line to ground causing the opposite terminal to go negative. The charge on Cs is then measured using an external resistor to ramp the negative terminal upwards until a zero crossing is achieved. The time required to zero cross becomes the measurement result.

The Cs capacitors should be connected as shown in Figure 1-1 on page 4. The value of these capacitors is not critical but 4.7 nF is recommended for most cases. They should be 10% X7R ceramic. If the transverse capacitive coupling from X to Y is large enough the voltage on a Cs capacitor can saturate, destroying gain. In such cases the burst length should be reduced and/or the Cs value increased. See Section 3.4.

If a Y line is not used its corresponding Cs capacitor may be omitted and the pins left floating.

## 3.4 Sample Capacitor Saturation

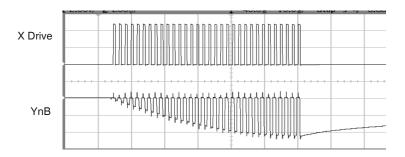

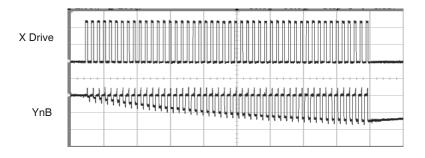

Cs voltage saturation at a pin YnB is shown in Figure 3.5. Saturation begins to occur when the voltage at a YnB pin becomes more negative than -0.25 V at the end of the burst. This nonlinearity is caused by excessive voltage accumulation on Cs inducing conduction in the pin protection diodes. This badly saturated signal destroys key gain and introduces a strong thermal coefficient which can cause phantom detection. The cause of this is either from the burst length being too long, the Cs value being too small, or the X-Y transfer coupling being too large. Solutions include loosening up the key structure interleaving, more separation of the X and Y lines on the PCB, increasing Cs, and decreasing the burst length.

Increasing Cs will make the part slower; decreasing burst length will make it less sensitive. A better PCB layout and a looser key structure (up to a point) have no negative effects.

Cs voltages should be observed on an oscilloscope with the matrix layer bonded to the panel material; if the Rs side of any Cs ramps more negative than -0.25 V during any burst (not counting overshoot spikes which are probe artifacts), there is a potential saturation problem.

#### Figure 3-2. VCs – Poor Gain, Nonlinear During Burst

Figure 3.5 shows a defective waveform similar to that of Figure 3.5, but in this case the distortion is caused by excessive stray capacitance coupling from the Y line to AC ground; for example, from running too near and too far alongside a ground trace, ground plane, or other traces. The excess coupling causes the charge-transfer effect to dissipate a significant portion of the received charge from a key into the stray capacitance. This phenomenon is more subtle; it can be best detected by increasing BL to a high count and watching what the waveform does as it descends towards and below -0.25 V. The waveform will appear deceptively straight, but it will slowly start to flatten even before the -0.25 V level is reached.

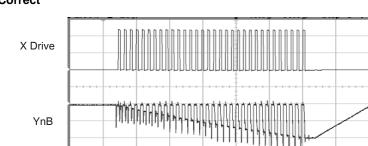

#### Figure 3-3. VCs – Correct

A correct waveform is shown in Figure 3.5 on page 10. Note that the bottom edge of the bottom trace is substantially straight (ignoring the downward spikes).

Unlike other QT circuits, the Cs capacitor values on QT2160 devices have no effect on conversion gain. However, they do affect conversion time.

Unused Y lines should be left open.

#### 3.5 Sample Resistors

The sample resistors (Rs0 – Rs1) are used to perform single-slope ADC conversion of the acquired charge on each Cs capacitor. These resistors directly control acquisition gain; larger values of Rs will proportionately increase signal gain. For most applications Rs should be 1 M $\Omega$ . Unused Y lines do not require an Rs resistor.

#### 3.6 Signal Levels

The signal values should normally be in the range of 200 to 750 counts with properly designed key shapes and values of Rs. However, long adjacent runs of X and Y lines can also artificially boost the signal values, and induce signal saturation; this is to be avoided. The X-to-Y coupling should come mostly from intra-key electrode coupling, not from stray X-to-Y trace coupling.

The signal swing from the smallest finger touch should preferably exceed 8 counts, with 12 being a reasonable target. The signal threshold setting (NTHR) should be set to a value guaranteed to be less than the signal swing caused by the smallest touch.

Increasing the burst length (BL) parameter will increase the signal strengths, as will increasing the sampling resistor (Rs) values.

## 3.7 Matrix Series Resistors

The X and Y matrix scan lines can use series resistors (Rx0 – Rx7 and Ry0 – Ry1 respectively) for improved EMC performance (Figure 1-1 on page 4).

X drive lines require Rx in most cases to reduce edge rates and thus reduce RF emissions. Values range from 1 k $\Omega$  to 20 k $\Omega$ , typically 1 k $\Omega$ .

Y lines need Ry to reduce EMC susceptibility problems and in some extreme cases, ESD. Typical Y values are about 1 k $\Omega$ . Y resistors act to reduce noise susceptibility problems by forming a natural low-pass filter with the Cs capacitors.

It is essential that the Rx and Ry resistors and Cs capacitors be placed very close to the chip. Placing these parts more than a few millimeters away opens the circuit up to high frequency interference problems (above 20 MHz) as the trace lengths between the components and the chip start to act as RF antennae.

The upper limits of Rx and Ry are reached when the signal level and hence key sensitivity are clearly reduced. The limits of Rx and Ry will depend on key geometry and stray capacitance, and thus an oscilloscope is required to determine optimum values of both.

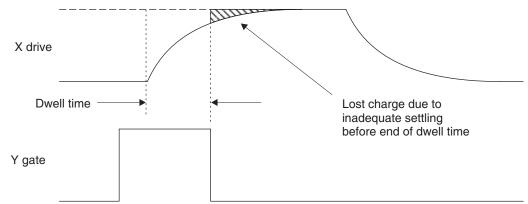

Dwell time is the duration in which charge coupled from X to Y is captured (Figure 3-4 on page 11). Increasing Rx values will cause the leading edge of the X pulses to increasingly roll off, causing the loss of captured charge (and hence loss of signal strength) from the keys.

The dwell time is a minimum of 250 ns. If the X pulses have not settled within 250 ns, key gain will be reduced; if this happens, either the stray capacitance on the X line(s) should be reduced (by a layout change, for example by reducing X line exposure to nearby ground planes or traces), or, the Rx resistor needs to be reduced in value (or a combination of both approaches).

One way to determine X line settling time is to monitor the fields using a patch of metal foil or a small coin over the key (Figure 3-5 on page 11). Only one key along a particular X line needs to be observed, 250 ns dwell time should exceed the observed 95% settling of the X-pulse by 25% or more.

In almost all cases, Ry should be set equal to Rx, which will ensure that the charge on the Y line is fully captured into the Cs capacitor.

#### Figure 3-5. Probing X-Drive Waveforms With a Coin

## 3.8 Key Design

Circuits can be constructed out of a variety of materials including conventional FR-4, Flexible Printed Circuit Boards (FPCB), silver silk-screened on PET plastic film, and even inexpensive punched single-sided CEM-1 and FR-2.

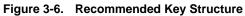

The actual internal pattern style is not as important as the need to achieve regular X and Y widths and spacings of sufficient size to cover the desired graphical key area or a little bit more; ~3mm oversize is acceptable in most cases, since the key's electric fields drop off near the edges anyway. The overall key size can range from 6 mm x 6 mm up to 100 mm x 100 mm but these are not hard limits. The keys can be any shape including round, rectangular, square, etc. The internal pattern can be interdigitated as shown in Figure 3-6.

For small, dense keypads, electrodes such as shown in the lower half of Figure 3-6 can be used. Where the panels are thin (under 2 mm thick) the electrode density can be quite high.

For better surface moisture suppression, the outer perimeter of X should be as wide as possible, and there should be no ground planes near the keys. The variable T in this drawing represents the total thickness of all materials that the keys must penetrate.

**Note:** *T* should ideally be similar to the complete thickness the fields need to penetrate to the touch surface. Smaller dimensions will also work but will give less signal strength. If in doubt, make the pattern coarser. The lower figure shows a simpler structure used for compact key layouts, for example for mobile phones. A layout with a common X drive and two receive electrodes is depicted

## 3.9 Setting the Slider

#### 3.9.1 Introduction

Groups of keys can be configured as a slider, in addition to their use as keys. The slider uses the Y0 line of the matrix and must start at X0, with the keys placed in consecutive numerical order. The slider can take up a programmable number of keys on the Y0 line. The remaining keys on that Y line behave as normal.

Positional data is calculated in a customizable range of 2 bits (0 - 3) to 8 bits (0 - 255). Geometric constraints may mean that the data will not reach the full range. Thinner dielectric or the use of more keys in a slider will increase the data range towards the ends.

Stability of the reported position will be dependent on the amount of signal on the slider keys. Running at higher resolutions, with a thick panel might produce a fluctuating reported position.

Key sizes should be in the 5 – 7mm range when used in the slider to get the best linearity. The slider should be made up of however many of these elements are required to fit their dimensions.

The slider will be treated as an object in the Adjacent Key Suppression (AKS) groupings. The keys in the slider would normally be set to the same burst length and threshold, although adjustments can be made in these at the expense of linearity.

#### 3.9.2 AKS Technology and the Slider

There can be up to three AKS groups, implemented so that only one key in each group may be reported as being touched at any one time. The AKS technique will lock onto the dominant key, and until this key is released, other keys in the group will not be reported as in detection. This allows a user to slide a finger across multiple keys with only the dominant key reporting touch. Each key may be in one of the groups 1 - 3, or in group 0 meaning that it is not AKS enabled.

Keys in the slider are not able to use AKS technique against each other. This is necessary to enable smooth scrolling. Multiple keys within the slider can be in detect at the same time, regardless of the AKS settings. The AKS technique will, however, work against keys outside the object or within another object. For example, if a slider is in the same AKS group as keys, then touching anywhere on the slider will cause the AKS technique to suppress the keys. Similarly touching the keys first will suppress the slider.

**Note:** For normal operation all keys in the slider should be placed in the same AKS group.

## 3.10 PCB Layout, Construction

#### 3.10.1 Overview

It is best to place the chip near the touch keys on the same PCB so as to reduce X and Y trace lengths, thereby reducing the chances for EMC problems. Long connection traces act as RF antennae. The Y (receive) lines are much more susceptible to noise pickup than the X (drive) lines.

Even more importantly, all signal related discrete parts (resistors and capacitors) should be very close to the body of the chip. Wiring between the chip and the various resistors and capacitors should be as short and direct as possible to suppress noise pickup.

Ground planes, if used, should be placed under or around the QT chip itself and the associated resistors and capacitors in the circuit, under or around the power supply, and back to a connector. Ground planes can be used to shield against radiated noise, but at the expense of a reduction in sensitivity as described previously.

**Note:** When using ground planes/floods, parasitic capacitance on Y lines can lead to reduced charge-transfer efficiency. For noise suppression, ground planes/floods can be beneficial around and between keys on the touch side of the PCB. However, it is advisable to route Y lines on the PCB layer furthest away from the plane/flood, to reduce parasitic capacitance. Cross-hatched ground patterns can act as effective shields, while helping to reduce parasitic capacitance. Ground planes/floods around the chip are generally acceptable, taking into account the same considerations as for the Y line parasitics.

#### 3.10.2 LED Traces and Other Switching Signals

Digital switching signals near the Y lines will induce transients into the acquired signals, deteriorating the SNR performance of the device. Such signals should be routed away from the Y lines, or the design should be such that these lines are not switched during the course of signal acquisition (bursts).

LED terminals which are multiplexed or switched into a floating state and which are within or physically very near a key structure (even if on another nearby PCB) should be bypassed to either Vss or Vdd with at least a 10 nF capacitor to suppress capacitive coupling effects which can induce false signal shifts. The bypass capacitor does not need to be next to the LED, in fact it can be quite distant. The bypass capacitor is noncritical and can be of any type.

LED terminals which are constantly connected to Vss or Vdd do not need further bypassing.

#### 3.10.3 Tracks

The central pad on the underside of the chip should be connected to ground. Do not run any tracks underneath the body of the chip, only ground.

#### Figure 3-7. Position of Tracks

**Example of GOOD tracking**

Example of BAD tracking

#### 3.10.4 PCB Cleanliness

All capacitive sensors should be treated as highly sensitive circuits which can be influenced by stray conductive leakage paths. QT devices have a basic resolution in the femtofarad range; in this region, there is no such thing as "clean flux". Flux absorbs moisture and becomes conductive between solder joints, causing signal drift and resultant false detections or transient losses of sensitivity or instability. Conformal coatings will trap in existing amounts of moisture which will then become highly temperature sensitive.

The designer should specify ultrasonic cleaning as part of the manufacturing process, and in cases where a high level of humidity is anticipated, the use of conformal coatings after cleaning to keep out moisture.

## 3.11 Power Supply Considerations

See Section 9.2 on page 43 for the Vdd range and short-term power supply fluctuations. If the power supply fluctuates slowly with temperature, the device will track and compensate for these changes automatically with only minor changes in sensitivity. If the supply voltage drifts or shifts quickly, the drift compensation mechanism will not be able to keep up, causing sensitivity anomalies or false detections.

As the device uses the power supply itself as an analog reference, the power should be very clean and come from a separate regulator. A standard inexpensive Low Dropout (LDO) type regulator should be used that is not also used to power other loads such as LEDs, relays, or other high current devices. Load shifts on the output of the LDO can cause Vdd to fluctuate enough to cause false detection or sensitivity shifts.

Caution: A regulator IC shared with other logic devices can result in erratic operation and is not advised.

A regulator can be shared among two or more QT devices on one board. Refer to page 4 for suggested regulator manufacturers.

A single ceramic 0.1  $\mu$ F bypass capacitor, with short traces, should be placed very close to supply pins 3 and 4 of the IC. Failure to do so can result in device oscillation, high current consumption, erratic operation, and so on. Pins 16 and 17 do not require bypassing if the traces between these pins and power traces are short.

Suggested regulator manufacturers:

- Toko (XC6215 series)

- Seiko (S817 series)

- BCDSemi (AP2121 series)

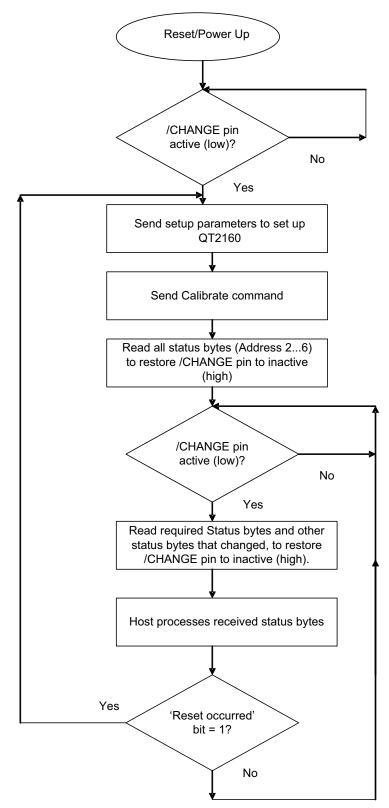

## 3.12 Startup/Calibration Times

The device requires initialization times of approximately 70 ms. The CHANGE line will go low and calibration will start (takes 15 matrix scans), after this start up period is over.

## 3.13 Calibration

Calibration does not occur periodically. Keys are only calibrated on power-up and when:

Enabled

AND

• held in detect for too long. The negative recalibration delay (NRD) period is specified by the user

OR

the signal delta value is greater than the positive threshold value, defined as reference value plus threequarters of the negative threshold

OR

• the user issues a recalibrate command

An interrupt on the  $\overline{CHANGE}$  pin occurs when there is a change in the key status bytes. An interrupt will occur on calibration only if at least one of the keys or objects was in detect as recalibration will then cause a status change.

## 3.14 Reset Input

The  $\overline{\text{RST}}$  pin can be used to reset the device to simulate a power-down cycle, in order to bring the device up into a known state should communications with the device be lost. The pin is active low, and a low pulse lasting at least 10µs must be applied to this pin to cause a reset.

If an external hardware reset is not used, the reset pin may be connected to Vdd.

## 3.15 Spread Spectrum Acquisitions

QT2160 uses spread-spectrum burst modulation. This has the effect of drastically reducing the possibility of EMI effects on the sensor keys, while simultaneously spreading RF emissions. This feature is hard-wired into the device and cannot be disabled or modified.

Spread spectrum is configured as a frequency chirp over a wide range of frequencies for robust operation.

## 3.16 Detection Integrator

See also Section 3.2 on page 8.

The device features a detection integration mechanism, which acts to confirm a detection in a robust fashion. A perkey counter is incremented each time the key has exceeded its threshold and stayed there for a number of acquisitions. When this counter reaches a preset limit the key is finally declared to be touched.

For example, if the limit value is 10, then the device has to exceed its threshold and stay there for 10 acquisitions in succession without going below the threshold level, before the key is declared to be touched. If on any acquisition the signal is not seen to exceed the threshold level, the counter is cleared and the process has to start from the beginning.

### 3.17 Sleep

The device operates on a fixed 16 ms cycle time basis. The device will perform a set of measurements and then sleep for the rest of the cycle to conserve power.

There are two user-configurable sleep modes; Low Power (LP) mode and SLEEP mode.

The LP setting (see Section 3.2 on page 8) is used for conserving power when there are no touches and is set to be a long time period. This will determine how often the device wakes up to do drift compensation. It also determines the maximum response time to the first touch after inactivity.

When a valid touch is registered, the device enters minimum cycle time (16 ms) for a faster response to key touch and object operation. The device will stay in this mode if it continues to see keys being touched and released. There is a user-selectable inactivity timeout; the awake timeout.

The measurement period needs to be shorter than the 16 ms fixed cycle time for optimum operation. If the measurement time exceeds the 16 ms fixed cycle time, a CYCLE OVERRUN bit is set in the general status register. The QT2160 will still operate if the 16 ms fixed cycle time is exceeded, but the timing for the timed parameters, for example, drift compensation negative recalibration time out, and so on, will slightly change.

A low power setting of zero causes the device to enter an ultra-low power mode (**SLEEP**), where no measurements are carried out. SLEEP mode also stops the internal watchdog timer, so that the part is totally dormant, and current drain is  $<2 \mu A$ . The PWM function will not be carried out during SLEEP, therefore it is recommended driving the GPIOs/GPOs to known states before entering SLEEP mode.

The QT2160 wakes from SLEEP mode if there is an address match on the  $I^2C$  bus, a hardware reset on the RST pin or an LP mode is set. If the Wake option is set for the dedicated GPIO inputs, then the QT2160 will trigger the CHANGE line if a change in status (either positive or negative going edge) of the respective GPIO is detected, in SLEEP mode.

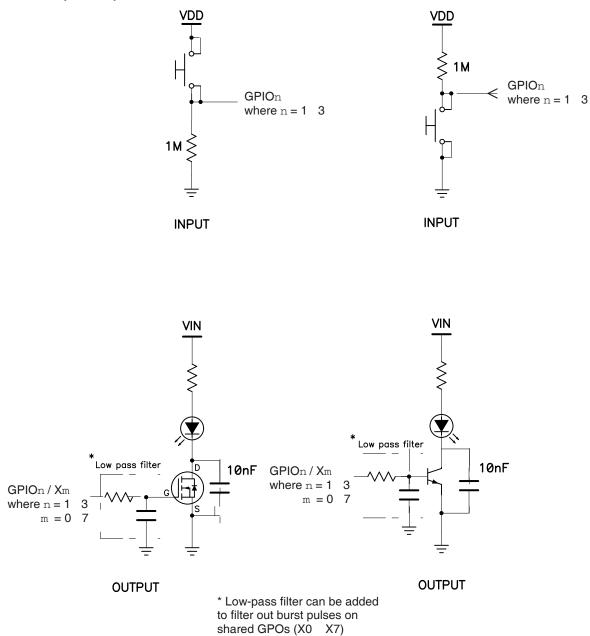

## 3.18 General Purpose Inputs/Outputs

There are three dedicated GPIOs (GPIO1 – 3) and eight GPOs shared with X lines (X0 – 7). Shared GPOs are always outputs, whereas dedicated GPIOs can be set to be outputs or inputs.

GPIOs set to input can be used for reading dome switches or logic signals. Outputs can be used to drive LEDs, or other devices. It is recommended driving external devices through the use of bipolar transistors or MOSFETs, so as not to affect capacitive sensing if a load fluctuates the power rail by drawing/sinking too much current.

All GPOs and GPIOs set to output can be PWM driven, if the corresponding PWM bit is set. Note that the PWM duty cycle will be an approximation, as GPIOs will not be switched during acquisition bursts.

The dedicated GPIOs have a Wake option, that if enabled will enable dedicated GPIOs set as inputs, to be read in SLEEP mode.

Note that shared GPOs (X0 – X7) are driven by the burst pulses during acquisition bursts, if the corresponding X line is used in the keys/slider. A low pass filter can be inserted to eliminate these burst pulses, as shown in Figure 1-2 on page 5.

## 4. I<sup>2</sup>C Operation

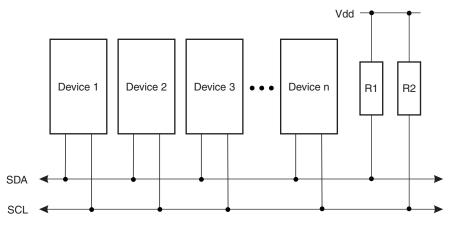

The device communicates with the host over an  $I^2C$  bus. The following sections give an overview of the bus; more detailed information is available from www.i2C-bus.org. Devices are connected to the  $I^2C$  bus as shown in Figure 4-1. Both bus lines are connected to Vdd via pull-up resistors. The bus drivers of all  $I^2C$  devices must be open-drain type. This implements a wired AND function that allows any and all devices to drive the bus, one at a time. A low level on the bus is generated when a device outputs a zero.

#### Figure 4-1. I<sup>2</sup>C Interface Bus

## 4.1 Transferring Data Bits

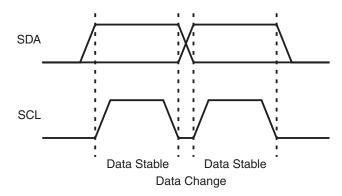

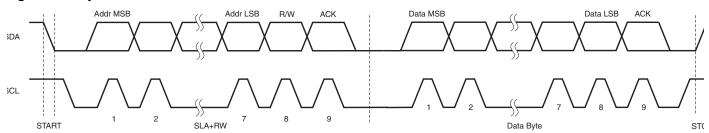

Each data bit transferred on the bus is accompanied by a pulse on the clock line. The level of the data line must be stable when the clock line is high; the only exception to this rule is for generating START and STOP conditions.

#### Figure 4-2. Data Transfer

## 4.2 START and STOP Conditions

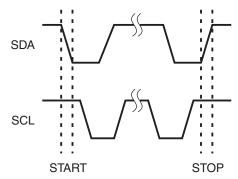

The host initiates and terminates a data transmission. The transmission is initiated when the host issues a START condition on the bus, and is terminated when the host issues a STOP condition. Between the START and STOP conditions, the bus is considered busy. As shown in Figure 4-3, START and STOP conditions are signaled by changing the level of the SDA line when the SCL line is high.

#### Figure 4-3. START and STOP Conditions

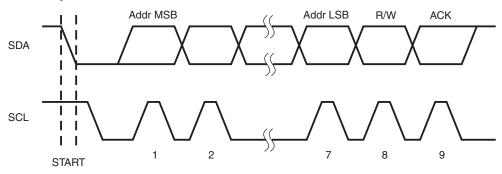

#### 4.3 Address Byte Format

All address bytes are 9 bits long, consisting of 7 address bits, one READ/WRITE control bit and an acknowledge bit. If the READ/WRITE bit is set, a read operation is performed, otherwise a write operation is performed. When the device recognizes that it is being addressed, it will acknowledge by pulling SDA low in the ninth SCL (ACK) cycle. An address byte consisting of a slave address and a READ or a WRITE bit is called SLA+R or SLA+W, respectively.

The most significant bit of the address byte is transmitted first. The address sent by the host must be consistent with that selected with the option jumpers.

#### Figure 4-4. Address Byte Format

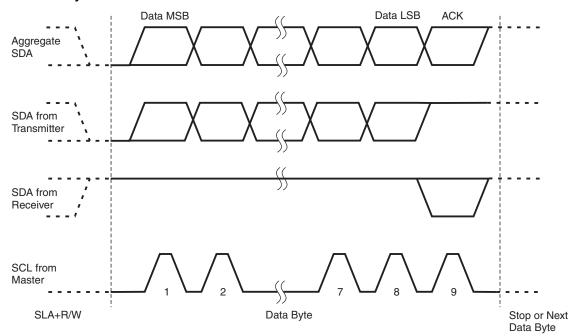

## 4.4 Data Byte Format

All data bytes are 9 bits long, consisting of 8 data bits and an acknowledge bit. During a data transfer, the host generates the clock and the START and STOP conditions, while the receiver is responsible for acknowledging the reception. An acknowledge (ACK) is signaled by the receiver pulling the SDA line low during the ninth SCL cycle. If the receiver leaves the SDA line high, a NACK is signaled.

## 4.5 Combining Address and Data Bytes into a Transmission

A transmission consists of a START condition, an SLA+R/W, one or more data bytes and a STOP condition. The wired *ANDing* of the SCL line is used to implement handshaking between the host and the device. The device extends the SCL low period by pulling the SCL line low whenever it needs extra time for processing between the data transmissions.

**Note:** Each write or read cycle must end with a stop condition. The device may not respond correctly if a cycle is terminated by a new start condition.

Figure 4-6 shows a typical data transmission. Note that several data bytes can be transmitted between the SLA+R/W and the STOP.

Figure 4-6. Byte Transmission

## 5. Interfaces

## 5.1 I<sup>2</sup>C Protocol

The I<sup>2</sup>C protocol is based around access to an address table and supports multi-byte reads and writes.

**Note:** Each write or read cycle must end with a stop condition. The QT2160 may not respond correctly if a cycle is terminated by a new start condition.

## 5.2 I<sup>2</sup>C Addresses

Four preset I<sup>2</sup>C addresses are selectable through pin I2CA0 and I2CA1 (Table 5-1).

| I2CA1 | I2CA0 | Address |

|-------|-------|---------|

| 0     | 0     | 0x0D    |

| 0     | 1     | 0x17    |

| 1     | 0     | 0x44    |

| 1     | 1     | 0x6B    |

## 5.3 Data Read/Write

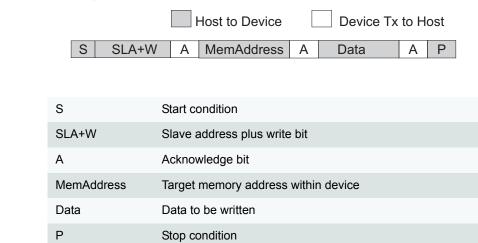

#### 5.3.1 Writing Data to the Device

The sequence of events required to write data to the device is shown next.

Key:

| The host initiates the transfer by sending the START condition, and follows this by sending the slave address of the |

|----------------------------------------------------------------------------------------------------------------------|

| device together with the Write-bit. The device sends an ACK. The host then sends the memory address within the       |

| device it wishes to write to. The device sends an ACK. The host transmits one or more data bytes; each will be       |

| acknowledged by the device.                                                                                          |

If the host sends more than one data byte, they will be written to consecutive memory addresses. The device automatically increments the target memory address after writing each data byte. After writing the last data byte, the host should send the STOP condition.

The host should not try to write beyond address 255 because the device will not increment the internal memory address beyond this.

#### 5.3.2 Reading Data From the Device

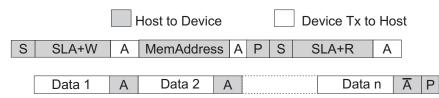

The sequence of events required to read data from the device is shown next.

The host initiates the transfer by sending the START condition, and follows this by sending the slave address of the device together with the Write-bit. The device sends an ACK. The host then sends the memory address within the device it wishes to read from. The device sends an ACK.

The host must then send a STOP and a START condition followed by the slave address again but this time accompanied by the Read-bit. The device will return an ACK, followed by a data byte. The host must return either an ACK or NACK. If the host returns an ACK, the device will subsequently transmit the data byte from the next address. Each time a data byte is transmitted, the device automatically increments the internal address. The device will continue to return data bytes until the host responds with a NACK. The host should terminate the transfer by issuing the STOP condition.

## 5.4 SDA, SCL

The  $I^2C$  bus transmits data and clock with SDA and SCL. They are open-drain; that is  $I^2C$  master and slave devices can only drive these lines low or leave them open. The termination resistors (Rp) pull the line up to Vdd if no  $I^2C$  device is pulling it down.

The termination resistors commonly range from 1 k $\Omega$  to 10 k $\Omega$  and should be chosen so that the rise times on SDA and SCL meet the I<sup>2</sup>C specifications (1 µs maximum).

#### 5.5 CHANGE Pin

The  $\overline{\text{CHANGE}}$  pin is an active low open drain output that can be used to alert the host of any changes to any of the 5 status bytes (address 2 to 6), thus reducing the need for wasteful I<sup>2</sup>C communications. After setting up the QT2160, the host can simply not communicate with the device, except when the  $\overline{\text{CHANGE}}$  pin goes active.

CHANGE goes inactive again only when the host performs a read from all status bytes which have changed.

Poll rate: The host can make use of the CHANGE pin output to initiate a communication; this will guarantee the optimal polling rate.

If the host cannot make use of the CHANGE pin, the poll rate should be no faster than once per matrix scan (see Section 9.4 on page 44). Anything faster will not provide new information and will slow down the chip operation.

The  $\overline{\text{CHANGE}}$  pin requires a pull-up resistor, with a typical value of ~100 k $\Omega$ .

## 6. Communications Protocol

## 6.1 Introduction

The device is address mapped. All communications consist of writes to, and reads from, locations in an 8-bit address map. Table 6-1 shows the address map of QT2160.

| Address | Use                      | Access     |

|---------|--------------------------|------------|

| 0       | Chip ID                  | Read       |

| 1       | Major/minor code version | Read       |

| 2       | General Status           | Read       |

| 3       | Key Status 1             | Read       |

| 4       | Key Status 2             | Read       |

| 5       | Slider Touch Position    | Read       |

| 6       | GPIO Read                | Read       |

| 7       | Sub-revision             | _          |

| 8 – 9   | Reserved – 0x00          | _          |

| 10      | Calibrate                | Read/Write |

| 11      | Reset                    | Read/Write |

| 12      | LP Mode                  | Read/Write |

| 13      | Burst Repetition         | Read/Write |

| 14      | Reserved – 0x00          | Read/Write |

| 15      | Neg Drift Compensation   | Read/Write |

| 16      | Pos Drift Compensation   | Read/Write |

| 17      | Normal DI Limit          | Read/Write |

| 18      | Neg Recal Delay          | Read/Write |

| 19      | Drift Hold Time/AWAKE    | Read/Write |

| 20      | Slider Control           | Read/Write |

| 21      | Slider Options           | Read/Write |

| 22 – 37 | Key 0 – 15 Key Control   | Read/Write |

| 38 – 53 | Key 0 – 15 Neg Threshold | Read/Write |

| 54 – 69 | Key 0 – 15 Burst Length  | Read/Write |

| 70      | GPIO/GPO Drive 1         | Read/Write |

| 71      | GPIO/GPO Drive 2         | Read/Write |

| 72      | Reserved - 0x00          | Read/Write |

| 73      | GPIO Direction 2         | Read/Write |

Table 6-1.Memory Map

| Address   | Use                   | Access     |

|-----------|-----------------------|------------|

| 74        | GPIO/GPO PWM 1        | Read/Write |

| 75        | GPIO/GPO PWM 2        | Read/Write |

| 76        | PWM Level             | Read/Write |

| 77        | GPIO Wake             | Read/Write |

| 78        | Common change Keys 1  | Read/Write |

| 79        | Common change Keys 2  | Read/Write |

| 80 – 99   | Reserved – 0x00       | -          |

| 100 – 131 | Key 0 – 15 Signals    | Read       |

| 132 – 163 | Key 0 – 15 References | Read       |

#### Table 6-1. Memory Map (Continued)

Note: Reserved areas can be read or written to, to simplify communications. If written to, only write 0x00.

## 6.2 Address 0: Chip ID

| Table 6-2. Chip ID |    |         |    |    |    |    |    |    |  |  |

|--------------------|----|---------|----|----|----|----|----|----|--|--|

| Address            | b7 | b6      | b5 | b4 | b3 | b2 | b1 | b0 |  |  |

| 0                  |    | Chip ID |    |    |    |    |    |    |  |  |

There is an 8-bit chip ID, which is set at 0x11.

#### 6.3 Address 1: Code Version

#### Table 6-3.Code Version

| Address | b7 | b6            | b5 | b4 | b3 | b2            | b1 | b0 |  |

|---------|----|---------------|----|----|----|---------------|----|----|--|

| 1       |    | Major Version |    |    |    | Minor Version |    |    |  |

There is an 8-bit major and minor version of firmware code revision. The top nibble of the firmware version register contains the major version (4.0) and the bottom nibble contains the minor version (4.0).

### 6.4 Address 2: General Status

| Address | b7    | b6               | b5 | b4 | b3 | b2 | b1 | b0   |

|---------|-------|------------------|----|----|----|----|----|------|

| 2       | RESET | CYCLE<br>OVERRUN | 0  | 0  | 0  | 0  | СС | SDET |

These bits indicate the general status of the device. A change in this byte will cause the CHANGE line to trigger.

**RESET:** this bit is set after a reset. This bit is clear after this byte is read back by the host.

**CYCLE OVERRUN:** this bit is set if the cycle time is more than 16 ms. It will be cleared when the cycle time is less than 16ms.

Note: holding any of the I<sup>2</sup>C lines, for clock stretching or other purposes, will increase the cycle time.

**CC:** this common change bit is set if all the selected keys (address 78 – 79) have a signal change of more than half the detection threshold, NTHR. The CC bit is not debounced.

This bit can be used to indicate a common change in signals, for example, in a notebook application, where the cover is closing, so that the host can suppress key detections.

Note: the CC bit will be set to 1 if no keys are selected to be in the Common Change group (see Section 6.27 on page 34).

SDET: this bit is set if a touch is detected on the slider.

## 6.5 Address 3 – 4: Key Status

Table 6-5.

Key Status and Numbering

| Address | b7  | b6  | b5  | b4  | b3  | b2  | b1 | b0 |

|---------|-----|-----|-----|-----|-----|-----|----|----|

| 3       | k7  | k6  | k5  | k4  | k3  | k2  | k1 | k0 |

| 4       | k15 | k14 | k13 | k12 | k11 | k10 | k9 | k8 |

#### Address 3: detect status for keys 0 - 7

#### Address 4: detect status for keys 8 - 15

Each location indicates all keys in detection, if any, as a bit field; touched keys report as 1, untouched or disabled keys report as 0. A change in this byte will cause the CHANGE line to trigger.

## 6.6 Address 5: Slider Touch Position

#### Table 6-6. Slider Touch Position

| Address | b7 | b6 | b5 | b4  | b3    | b2 | b1 | b0 |

|---------|----|----|----|-----|-------|----|----|----|

| 5       |    |    |    | Pos | ition |    |    |    |

Position: Last position of the touch on the slider

A change in this byte will cause the CHANGE line to trigger.

## 6.7 Address 6: GPIO Read

Table 6-7. GPIO Read

| Address | b7 | b6 | b5 | b4    | b3    | b2    | b1 | b0 |

|---------|----|----|----|-------|-------|-------|----|----|

| 6       | 0  | 0  | 0  | GPIO3 | GPIO2 | GPIO1 | 0  | 0  |

**GPIO1 – 3:** If GPIO1 – 3 are set as inputs, returns the logic level on the respective pin. If a GPIO is set as an output, the respective bit in GPIO Read will always report 0.

GPIOs set as inputs are only read once every cycle, that is, every 16ms.

A change in this byte will cause the  $\overline{CHANGE}$  line to trigger.

## 6.8 Address 7: Sub-revision

This is an 8-bit sub-revision number that follows the code version (for example, 4.0.0).

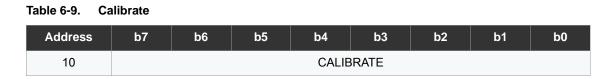

## 6.9 Address 10: Calibrate

Writing any non-zero value into this address will trigger the QT2160 to start a recalibration on all enabled keys.

## 6.10 Address 11: Reset

Any non-zero value will trigger the device to reset. After a reset, the device will revert to default settings.

After receiving a reset command the QT2160 will start not acknowledging  $I^2C$  communications and make CHANGE inactive within 16ms. The chip will reset after another ~16ms.

## 6.11 Address 12: LP Mode

| Table 6-11. LP M |

|------------------|

|------------------|

| Address | b7 | b6 | b5 | b4   | b3   | b2 | b1 | b0 |

|---------|----|----|----|------|------|----|----|----|

| 12      |    |    |    | LP_N | IODE |    |    |    |

LP mode sets the sleep time between bursts. A higher value causes more sleep time between acquisitions resulting in lower power consumption, but slower response time.

The values are between 1 and 255, with each incrementing the sleep time by 16 ms steps. For example, 1 = 16 ms LP, 2 = 32 ms LP, 3 = 48 ms LP, and so on.

A value of zero causes the device to enter an ultra-low power mode (SLEEP), where no measurements are carried out (see Section 3.17 on page 17).

The QT2160 is designed to sleep as much as possible to conserve power.

**Note:** the longer the LP mode, the longer the response time at first touch. The response time for the first touch includes the digital filter settling time (a few measurement cycles) and the DI process. Above 256 ms LP mode the power consumption does not reduce as much, even with longer LP mode durations. Refer to Table 9-1 on page 45 for typical power consumptions.

Default value: 1 (6ms LP)

## 6.12 Address 13: Burst Repetition

| Table 6-12. | Burst Repetition |

|-------------|------------------|

|-------------|------------------|

| Address | b7 | b6 | b5 | b4 | b3 | b2  | b1 | b0 |

|---------|----|----|----|----|----|-----|----|----|

| 13      | 0  | 0  |    |    | BR | REP |    |    |

Burst Repetition (BREP) is a feature that enables the QT2160 to make multiple measurements and take the average result; this improves the device's ability to operate in noisy environments.

The number of burst repetitions can be reduced in low noise environments for faster response time. The BREP value can range between 1 and 63 repetitions. Do not set to 0 as it is not valid.

Default value: 1 (one measurement burst)

## 6.13 Address 15...16: Neg/Pos Drift Compensation

| Table 6-13. Neg/Pos Drift Compensation |

|----------------------------------------|

|----------------------------------------|

| Address | b7 | b6 | b5 | b4 | b3     | b2 | b1 | b0 |

|---------|----|----|----|----|--------|----|----|----|

| 15      | 0  |    |    |    | NDRIFT |    |    |    |

| 16      | 0  |    |    |    | PDRIFT |    |    |    |

Signals can drift because of changes in Cx and Cs over time and temperature. It is crucial that such drift be compensated, else false detections and sensitivity shifts can occur.

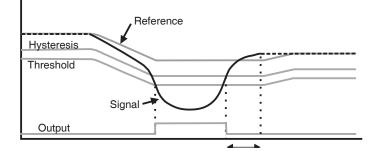

Drift compensation (see Figure 6-1) is performed by making the reference level track the raw signal at a slow rate, but only while there is no detection in effect. The rate of adjustment must be performed slowly, otherwise legitimate detections could be ignored. The parameters can be configured in increments of 0.16s.

#### Figure 6-1. Thresholds and Drift Compensation

The device drift compensates using a slew-rate limited change to the reference level; the threshold and hysteresis values are slaved to this reference.

When a finger is sensed, the signal falls since the human body acts to absorb charge from the cross-coupling between X and Y lines. An isolated, untouched foreign object (a coin, or a water film) will cause the signal to rise very slightly due to an enhancement of coupling. This is contrary to the way most capacitive sensors operate.

Once a finger is sensed, the drift compensation mechanism ceases since the signal is legitimately detecting an object. Drift compensation only works when the signal in question has not crossed the negative threshold level.

The drift compensation mechanism can be asymmetric; the drift-compensation can be made to occur in one direction faster than it does in the other simply by changing the NDRIFT and PDRIFT Setup parameters. This is a global configuration.

Specifically, drift compensation should be set to compensate faster for increasing signals than for decreasing signals. Decreasing signals should not be compensated quickly, since an approaching finger could be compensated for partially or entirely before even touching the touchpad (NDRIFT).

However, an obstruction over the sense pad, for which the sensor has already made full allowance, could suddenly be removed leaving the sensor with an artificially suppressed reference level and thus become insensitive to touch. In this latter case, the sensor should compensate for the object's removal by raising the reference level relatively quickly (PDRIFT).

Drift compensation and the detection time-outs work together to provide for robust, adaptive sensing. The time-outs provide abrupt changes in reference calibration depending on the duration of the signal event.

If PDRIFT or NDRIFT is set to 0 then the drift compensation in the respective direction is disabled.

**Note:** it is recommended that the drift compensation rate be more than four times the LP mode period. This is to prevent undersampling, which decreases the algorithm's efficiency.

| Default NDRIFT: | 20 (3.2 s/reference level) |

|-----------------|----------------------------|

| Default PDRIFT: | 5 (0.8 s/reference level)  |

## 6.14 Address 17: Detect Integrator

#### Table 6-14. Detect Integrator

| Address | b7 | b6 | b5 | b4 | b3 | b2   | b1 | b0 |

|---------|----|----|----|----|----|------|----|----|

| 17      | 0  | 0  | 0  |    |    | NDIL |    |    |

NDIL is used to provide signal filtering.

To suppress false detections caused by spurious events like electrical noise, the device incorporates a 'detection integrator' or DI counter mechanism. A per-key counter is incremented each time the key has exceeded its threshold and stayed there for a number of acquisitions in succession, without going below the threshold level. When this counter reaches a preset limit the key is finally declared to be touched.

If on any acquisition the signal is not seen to exceed the threshold level, the counter is cleared and the process has to start from the beginning.

The QT2160 has a built in minimum of 1 DI counts in addition to the NDIL value. Therefore, if setting a NDIL value of 3, the actual number of consecutive acquisitions is 4.

Available NDIL values are from 1 to 31.

Default: 3 (4 DI value)

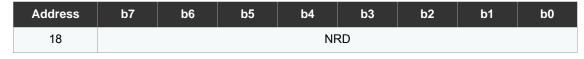

## 6.15 Address 18: Negative Recal Delay

#### Table 6-15. Negative Recal Delay

If an object unintentionally contacts a key resulting in a detection for a prolonged interval it is usually desirable to recalibrate the key in order to restore its function, perhaps after a time delay of some seconds.

The Negative Recal Delay timer monitors such detections; if a detection event exceeds the timer's setting, the key will be automatically recalibrated. After a recalibration has taken place, the affected key will once again function normally even if it is still being contacted by the foreign object. This feature is set globally.

NRD can be disabled by setting it to zero (infinite timeout) in which case the key will never auto-recalibrate during a continuous detection (but the host could still command it).

NRD is set globally, which can range in value from 1 to 255. NRD above 0 is expressed in 0.16 s increments.

**Default:** 255 (40.8 s)

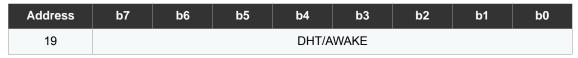

## 6.16 Address 19: Drift Hold Time/Awake Timeout

#### Table 6-16. Drift Hold Time/Awake Timeout

The DHT/AWAKE value is used for Drift Hold Time and Awake Timeout parameters.

#### Drift Hold Time (DHT)

This is used to restrict drift on all keys while one or more keys are activated. DHT defines the length of time the drift is halted after a key detection.

This feature is particularly useful in cases of high-density keypads where touching a key or hovering a finger over the keypad would cause untouched keys to drift, and therefore create a sensitivity shift, and ultimately inhibit any touch detection.

#### Awake Timeout (AWAKE)

After each matrix scan, the part will automatically go to sleep whenever possible to conserve power, unless there has been a key state change. The AWAKE timeout feature determines how long the device will remain in the minimum LP mode from the last key state change.

Subsequent key state changes reinitialize the AWAKE interval. Once the part has been awakened by a change, the key response time will be fast for as long as the keyboard remains in use. Once key activity lapses for a period longer than the AWAKE timeout, the part will return to the assigned LP mode.

DHT/AWAKE can be configured to a value of between 0.32s and 40.8s, in increments of 0.16s. Values of 0 and 1 are invalid and should not be used.

**Note:** It is recommended having a DHT/AWAKE of at least two seconds to prevent unintended key sensitivity drifts and the slider being unresponsive in longer LP modes.

DHT/AWAKE Default: 25 (4 s)

## 6.17 Address 20: Slider Control

**HSYT:** Set the hysteresis value for the slider's reported position. Hysteresis is the number of positions the user has to move back, before the new touch position is reported when the direction of scrolling is changed and during first scroll after touch down.

At lower resolutions, where skipping of reported positions will be noticed, hysteresis can be set to 0 (1 position). At higher resolutions (6 - 8 bits), it would be recommended to have a hysteresis of at least 2 positions or more.

HYST can range from 0 (1 position) to 15 (16 positions). The hysteresis is carried out at 8 bits resolution internally and scaled to the desired resolution; therefore at resolutions lower than 8 bits, there might be a difference of 1 reported position from the HYST setting, depending on where the touch down is.

**Note:** it is not valid to have a hysteresis value more than the available positions in a resolution. For example, do not have a HYST of 5 positions with a resolution of 2 bits (4 positions).

**NUM\_KEYS:** Set the number of keys to be used in the slider. For proper slider operation, valid values are between 2 and 8. Setting a value of 0, will disable the slider.

HYST Default: 0 (1 position),

NUM\_KEYS Default: 5 (5 keys)

## 6.18 Address 21: Slider Options

#### Table 6-18. Slider Options

| Address | b7 | b6 | b5 | b4 | b3 | b2         | b1 | b0 |

|---------|----|----|----|----|----|------------|----|----|

| 21      | 0  | 0  | 0  | 0  | 0  | RESOLUTION |    |    |

**RESOLUTION:** Resolution of reported position of touch on the slider. Valid values are between 0 (8 bits) to 6 (2 bits). The keys used for the slider starts at X0 and is on the Y0 line.

#### Table 6-19. Resolution

| Value | Resolution     | Value | Resolution      |

|-------|----------------|-------|-----------------|

| 0     | 8 bits (0-255) | 4     | 4 bits (0 – 15) |

| 1     | 7 bits (0-127) | 5     | 3 bits (0 – 7)  |

| 2     | 6 bits (0-63)  | 6     | 2 bits (0 – 3)  |

| 3     | 5 bits (0-31)  |       |                 |

**Note:** For better stability of the reported position at higher resolutions, increase the number of keys used to construct the slider, reduce the front panel thickness, reduce the loading on the slider keys or increase the burst length to gain more signal.

Default: 4 (4 bits)

## 6.19 Address 22 – 37: Key Control

#### Table 6-20. Key Control

| Address | b7 | b6 | b5 | b4 | b3 | b2 | b1        | b0 |

|---------|----|----|----|----|----|----|-----------|----|

| 22 – 37 | 0  | 0  | 0  | 0  | 0  | 0  | AKS GROUP |    |

**AKS GROUP:** these bits configure which AKS group a key is within (0 - AKS disabled, 1, 2 or 3). Keys in the same group cannot both be in detect at the same time, unless they both form part of the slider (see Section 3.9.2 on page 14).

**Default:** 0 (AKS disabled)

## 6.20 Address 38 – 53: Negative Threshold

Table 6-21. Negative Threshold

| Address | b7 | b6 | b5 | b4    | b3    | b2 | b1 | b0 |

|---------|----|----|----|-------|-------|----|----|----|

| 38 – 53 |    |    |    | THRES | SHOLD |    |    |    |

The negative threshold value is established relative to a key signal reference value. The threshold is used to determine key touch when crossed by a negative-going signal swing after having been filtered by the detection integrator. Larger absolute values of threshold desensitize keys since the signal must travel farther in order to cross the threshold level.

Conversely, lower thresholds make keys more sensitive.

As Cx and Cs drift, the reference point drift-compensates for these changes at a user-settable rate; the threshold level is recomputed whenever the reference point moves, and thus it also is drift compensated.

The amount of NTHR required depends on the amount of signal swing that occurs when a key is touched. Thicker panels or smaller key geometries reduce *key gain*, that is, signal swing from touch, thus requiring smaller NTHR values to detect touch.

**Negative hysteresis:** this is fixed at two less than the negative threshold value and cannot be altered. It is implemented to stop keys from dithering in and out of detect.

| NTHR Typical values: | 7 to 12                     |

|----------------------|-----------------------------|

| NTHR Default value:  | 10 (10 counts of threshold) |

## 6.21 Address 54 – 69: Burst Length

Table 6-22. Burst Length

|         | J  |    |    |         |       |    |    |    |

|---------|----|----|----|---------|-------|----|----|----|

| Address | b7 | b6 | b5 | b4      | b3    | b2 | b1 | b0 |

| 54 – 69 |    |    |    | BURST I | ENGTH |    |    |    |

The QT2160 uses a fixed number of pulses which are executed in burst mode. This number is set in groups of four. Therefore, the value send to the QT2160 is multiplied by four to get the actual number of burst pulses.

The burst length is the number of times the charge-transfer (QT) process is performed on a given key. Each QT process is simply the pulsing of an X line once, with a corresponding Y line enabled to capture the resulting charge passed through the key capacitance Cx.

Increasing burst length directly affects key sensitivity. This occurs because the accumulation of charge in the charge integrator is directly linked to the burst length. The burst length of each key can be set individually, allowing for direct digital control over the signal gains of each key individually.

Apparent touch sensitivity is also controlled by the Negative Threshold level (NTHR). Burst length and NTHR interact; normally burst lengths should be kept as short as possible to reduce scan time and limit RF emissions, but NTHR should be kept above 6 to reduce false detections due to external noise. The detection integrator mechanism also helps to prevent false detections.

Note: setting a burst length of zero for a specific key, disables that key.

| Typical values: | 8 – 32 (32 – 128 burst pulses) |

|-----------------|--------------------------------|

|                 |                                |

Default: 4 (16 burst pulses)

## 6.22 Address 70 - 71: GPIO/GPO Drive

| Address | b7 | b6 | b5 | b4    | b3    | b2    | b1 | b0 |

|---------|----|----|----|-------|-------|-------|----|----|

| 70      | X7 | X6 | X5 | X4    | Х3    | X2    | X1 | X0 |

| 71      | 0  | 0  | 0  | GPIO3 | GPIO2 | GPIO1 | 0  | 0  |

Table 6-23. GPIO/GPO Drive

If the GPIOs are set to outputs, the drive for the individual GPIO is set according to the corresponding bit in GPIO Drive bytes. Setting the bit to 1 will drive the corresponding GPIO pin to Vdd, while setting it to 0, will drive the corresponding GPIO pin to ground.

Enabling PWM on a GPIO pin will override the drive on the pin.

Shared X line GPOs will be only driven when not doing any measurements. During measurements, burst pulses will be driven from the X lines, make sure that the driven device will not be affected.

**Default:** 0 (All driven low)

## 6.23 Address 73: GPIO Direction

#### Table 6-24. GPIO Direction

| Address | b7 | b6 | b5 | b4    | b3    | b2    | b1 | b0 |

|---------|----|----|----|-------|-------|-------|----|----|

| 73      | 0  | 0  | 0  | GPIO3 | GPIO2 | GPIO1 | 0  | 0  |

Sets the direction of the GPIOs: 1 = driven outputs, 0 = floating inputs.

If set as inputs, the GPIO will only be read every 16ms (fixed cycle time).

Shared X line GPOs are always outputs. By default, the dedicated GPIOs are set as inputs. Make sure to drive (set to outputs) these GPIOs if not used, as floating pins may consume unnecessary current.

**Default:** 0 (All inputs)

## 6.24 Address 74 – 75: GPIO/GPO PWM

| Address | b7 | b6 | b5 | b4    | b3    | b2    | b1 | b0 |

|---------|----|----|----|-------|-------|-------|----|----|

| 74      | X7 | X6 | X5 | X4    | X3    | X2    | X1 | X0 |

| 75      | 0  | 0  | 0  | GPIO3 | GPIO2 | GPIO1 | 0  | 0  |

#### Table 6-25. GPIO/GPO PWM

Setting the corresponding GPIO PWM bit to 1 will enable PWM on the respective pin. The pin will be driven according to the duty cycle specified in PWM Level (address 76).

PWM will only be enabled on GPIOs that have their GPIO direction set to 1 (output).

Shared X line GPOs will only be driven when not doing any measurements. During measurements, burst pulses will be driven from the X lines, making sure that the driven device will not be affected.

All PWM enabled GPIOs/GPOs will only be switched when not doing any measurements. Therefore, the PWM duty cycle's accuracy will depend on the burst lengths of keys, as the longer the burst length, the longer the periods of no PWM switching.

**Default:** 0 (PWM disabled)

## 6.25 Address 76: PWM Level

Table 6-26. PWM Level

| Address | b7 | b6 | b5 | b4   | b3   | b2 | b1 | b0 |

|---------|----|----|----|------|------|----|----|----|

| 76      |    |    |    | DUTY | _CYC |    |    |    |

This sets the Duty Cycle of the PWM enabled pins. Valid values are between 0 to 255. A value of 0 - 10 will be 100% duty cycle (always on), and a value of 250 - 255 will be 0 percent duty cycle (always off).

**Default:** 0 (100% duty cycle)

## 6.26 Address 77: GPIO Wake

#### Table 6-27. GPIO Wake

| Address | b7 | b6 | b5 | b4    | b3    | b2    | b1 | b0 |

|---------|----|----|----|-------|-------|-------|----|----|

| 77      | 0  | 0  | 0  | GPIO3 | GPIO2 | GPIO1 | 0  | 0  |

If the corresponding bit is set to 1, dedicated GPIO pins set to inputs will still be read during SLEEP mode (no capacitive sensing carried out). When a change in the state of the inputs is detected, the CHANGE line will be triggered and the QT2160 will go back to SLEEP.

**Default:** 0 (Wake disabled)

## 6.27 Address 78 – 79: Common Change Keys

#### Table 6-28. Common Change Keys

| Address | b7  | b6  | b5  | b4  | b3  | b2  | b1 | b0 |

|---------|-----|-----|-----|-----|-----|-----|----|----|

| 78      | k7  | k6  | k5  | k4  | k3  | k2  | k1 | k0 |

| 79      | k15 | k14 | k13 | k12 | k11 | k10 | k9 | k8 |

**k0 – k15:** represents the respective keys. If set to 1, the respective key is included in the common change comparisons.

Note: if no keys are included in the Common Change group, the CC bit is set to 1.

**Default:** 0 (not included)

## 6.28 Address 100 – 163: Signals and References

Addresses 100 – 131 allow signal data to be read for each key. There are two bytes of data for each key. These are the key 16-bit signal which is accessed as two 8-bit bytes, stored LSB first.

Addresses 132 – 163 allow reference data to be read for each key. There are two bytes of data for each key. These are the key 16-bit reference which is accessed as two 8-bit bytes, stored LSB first.

There are a total of 16 keys and 4 bytes of data per key, yielding a total of 64 addresses. These addresses are readonly.

| Address   | b7  | b6         | b5        | b4     | b3            |

|-----------|-----|------------|-----------|--------|---------------|

| 100       | 0   | Signal LSB | 132       | 0      | Reference LSB |

| 101       | 0   | Signal MSB | 133       | 0      | Reference MSB |

| 102       | 1   | Signal LSB | 134       | 1      | Reference LSB |

| 103       | 1   | Signal MSB | 135       | 1      | Reference MSB |

| 104 – 131 | 215 |            | 136 – 163 | 2 – 15 |               |

Table 6-29.

Signal and References

## 7. Setups Block

Setups data is sent from the host to the Q160 using the I<sup>2</sup>C interface. The setups block is memory mapped onto this interface. Thus each setup can be accessed by reading/writing the appropriate address. Setups can be accessed individually or as a block.

| Address | Bytes          | Parameter                           | Symbol     | Valid<br>Range | Bits   | Key<br>Scope | Default<br>Value                                                                                    | Description                                                                                            | Page |

|---------|----------------|-------------------------------------|------------|----------------|--------|--------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|

| 12      | 1              | LP Mode                             | LP_MODE    | 0 – 255        | 8      | 16           | 1                                                                                                   | 0: SLEEP mode (no capacitive<br>sensing)<br>1 – 255: Low Power mode,<br>increments in steps of 16 ms   | 26   |

| 13      | 1              | Burst<br>Repetition                 | BREP       | 1 – 63         | 6      | 16           | 1                                                                                                   | Range is 1 – 63 burst repetitions                                                                      | 27   |

| 15      | 1              | Neg Drift<br>Comp                   | NDRIFT     | 0 – 127        | 7      | 16           | 20                                                                                                  | Range is in 0.16 s increments,<br>1 = 0.16 s/reference level                                           | 27   |

| 16      | 1              | Pos Drift Comp                      | PDRIFT     | 0 – 127        | 7      | 16           | 5                                                                                                   | Range is in 0.16 s increments,<br>1 = 0.16 s/reference level                                           | 27   |

| 17      | 1              | Normal DI<br>Limit                  | NDIL       | 1 – 31         | 5      | 16           | 3                                                                                                   | Normal DI limit: take the operand and add 2 to get the value                                           | 28   |

| 18      | 1              | Neg recal<br>delay                  | NRD        | 0 – 255        | 8      | 16           | 255 (40.8 s)                                                                                        | Range is in 0.16 s increments;<br>0 = infinite; default = 40.8 s<br>Range is {infinite, 0.16 – 40.8 s} | 29   |

| 19      | 1              | Drift Hold<br>Time/Awake<br>Timeout | DHT/AWAKE  | 2 – 255        | 8      | 16           | 25 (4s)                                                                                             | Range in 0.2 s increments;<br>default = 4 s                                                            | 29   |

|         |                |                                     | HYST       | 0 – 15         | 4      | Slider       | 0<br>(1 position)                                                                                   | 0 – 8: hysteresis for slider reported position                                                         |      |

| 20 1    | Slider Control | NUM_KEYS                            | 0, 2 – 8   | 4              | Slider | 5 (5 keys)   | 0: disables slider mode<br>2 – 8: number of keys in slider<br>Slider Keys start at X0 and are on Y0 | 30                                                                                                     |      |

| 21      | 1              | Slider Options                      | RESOLUTION | 0 – 6          | 3      | Slider       | 25 (4 s)                                                                                            | Resolution of reported slider touch<br>position<br>8 bits (0) to 2 bits (6)                            | 31   |

| 22 – 37 | 16             | Key Control                         | KEY_CONT   | 0 – 3          | 3      | 1            | 0 (AKS off)                                                                                         | 0: AKS disabled<br>1 – 3: AKS groups                                                                   | 31   |

| 38 – 53 | 16             | Neg threshold                       | NTHR       | 1 – 255        | 8      | 1            | 10                                                                                                  |                                                                                                        | 32   |

| 54 – 69 | 16             | Burst Length                        | BL         | 0 – 255        | 8      | 1            | 4<br>(16 pulses)                                                                                    | 0: Key disabled<br>1 – 255: Burst length = BL × 4                                                      | 32   |

#### Table 7-1. Setups Table

#### Table 7-1. Setups Table (Continued)

| Address | Bytes | Parameter      | Symbol          | Valid<br>Range | Bits  | Key<br>Scope | Default<br>Value | Description                                  | Page                        |    |

|---------|-------|----------------|-----------------|----------------|-------|--------------|------------------|----------------------------------------------|-----------------------------|----|

|         |       |                | X7              | 0 – 1          | 1     |              | 0                |                                              |                             |    |

|         |       |                | X6              | 0 – 1          | 1     | _            | 0                | -                                            |                             |    |

|         |       |                | X5              | 0 – 1          | 1     | -            | 0                |                                              |                             |    |

| 70      | 1     | GPO Drive 1    | X4              | 0 – 1          | 1     | _            | 0                | 0: GPO driven low                            | 33                          |    |

| 70      | 1     | GFO Drive I    | X3              | 0 – 1          | 1     | _            | 0                | 1: GPO driven high                           |                             |    |

|         |       |                | X2              | 0 – 1          | 1     | _            | 0                |                                              |                             |    |

|         |       |                | X1              | 0 — 1          | 1     | -            | 0                |                                              |                             |    |

|         |       |                | X0              | 0 – 1          | 1     | _            | 0                |                                              |                             |    |

|         |       |                | -               | _              | 1     | -            | 0                | _                                            |                             |    |

|         |       |                | -               | _              | 1     | -            | 0                |                                              |                             |    |

|         |       |                | -               | _              | 1     | -            | 0                |                                              |                             |    |

| 71      | 1     | GPIO Drive 2   | GPIO3           | 0 – 1          | 1     | -            | 0                | If GPIO set to output,<br>0: GPIO driven low | 33                          |    |

| 7.1     | 1     |                | GPIO2           | 0 – 1          | 1     | -            | 0                | 1: GPIO driven high                          |                             |    |

|         |       |                | GPIO1           | 0 – 1          | 1     | -            | 0                |                                              |                             |    |

|         |       |                | -               | _              | 1     | -            | 0                | _                                            |                             |    |

|         |       |                | -               | _              | 1     | -            | 0                |                                              |                             |    |

|         |       |                |                 | -              | _     | 1            | -                | 0                                            | _                           |    |

|         |       |                | -               | _              | 1     | -            | 0                |                                              | 33                          |    |

|         |       |                | -               | _              | 1     | -            | 0                | _                                            |                             |    |

| 73      | 1     | GPIO Direction | GPIO3           | 0 – 1          | 1     | -            | 0                | 0: GPIO is floating input                    |                             |    |

| 15      |       | 1              | Of TO Direction | GPIO2          | 0 – 1 | 1            | _                | 0                                            | 1: GPIO is push-pull output | 33 |

|         |       |                | GPIO1           | 0 – 1          | 1     | _            | 0                |                                              |                             |    |